# Investigating the inhibition of short channel effects using different materials of gate insulator layers in FinFET

#### Haotian Yu

School of Engineering and Informatics, University of Sussex, Brighton, BN1 9RJ, United Kingdom

hy263@sussex.ac.uk

Abstract. As the evolution of FinFET technology continues, traditional gate insulator materials, such as SiO<sub>2</sub>, face challenges in meeting the demands of modern applications, especially when it comes to gate leakage current control. Emerging as promising contenders to replace SiO<sub>2</sub>, materials with higher dielectric constants, notably HfO<sub>2</sub> and Si<sub>3</sub>N<sub>4</sub>, are drawing significant attention in the semiconductor community. Leveraging the advanced capabilities of tools like Silvaco TCAD, an in-depth analysis was conducted to compare the performance and gate leakage current control abilities of SiO<sub>2</sub>, HfO<sub>2</sub>, and Si<sub>3</sub>N<sub>4</sub>, utilizing the Quantum examples 3D FinFET model. The findings not only highlight the potential of HfO<sub>2</sub> and Si<sub>3</sub>N<sub>4</sub> as worthy replacements for SiO<sub>2</sub> but also accentuate the distinct advantages of SiO<sub>2</sub>, making it particularly well-suited as a substitute. This exploration goes beyond a mere comparison of materials. It dives deep into understanding their behaviors under various operational conditions, laying a foundation for potential breakthroughs and fostering the next wave of innovations in semiconductor technology.

**Keywords:** HfO<sub>2</sub>, Si<sub>3</sub>N<sub>4</sub>, SiO<sub>2</sub>, Performance, Gate Leakage Current Control Ability.

## 1. Introduction

With the continual progression of digital integrated circuits, there's an observable rapid enhancement in the performance of electronic semiconductor devices [1, 2]. One of the main driving forces behind this evolution has been the relentless pursuit of miniaturization. As these circuits become increasingly compact, they promise greater efficiency, speed, and power. Yet, the journey towards achieving smaller dimensions isn't without its challenges. One of the pronounced obstacles is the short channel effect. As transistors are scaled down, the gate's control ability tends to diminish. This phenomenon poses significant hurdles in maintaining the desired operational characteristics of these transistors [3]. Addressing this requires a comprehensive strategy, and one promising approach is the exploration of alternative materials. By shifting away from traditional materials, it might be possible to not only mitigate some of these miniaturization-induced issues but also to chart a path for further advancements, ensuring that the semiconductor industry remains at the cutting edge of technological innovation. SiO<sub>2</sub> has been the mainstream material for gate insulator layers for a long time, however, under the nanoscale demand, its production difficulty has increased significantly, and its performance is also difficult to meet the requirements [4, 5]. At the same time, when the thickness of the gate oxide becomes less and less, the problem of gate leakage will occur due to quantum tunneling [6], Short channel effects can lead to

<sup>© 2024</sup> The Authors. This is an open access article distributed under the terms of the Creative Commons Attribution License 4.0 (https://creativecommons.org/licenses/by/4.0/).

performance degradation and ultimately limit scaling [7]. Perhaps  $SiO_2$  is no longer the most suitable material for the gate insulator layers of FinFET, and for many other transistor structures,  $HfO_2$  and  $Si_3N_4$  performed well in terms of performance and suppression of short channel effects.

## 2. Relevant Theories

# 2.1. Some characteristics of $SiO_2$ , $Si_3N_4$ and $HfO_2$

As mentioned in the introduction, most existing processes use a silicon dioxide layer as the gate dielectric, silicon dioxide is mainly composed of glass, crystal, and quartz, it is a good insulator, at the same time, it also has good thermal and electrical stability, good interface quality, and good electrical isolation performance [8, 9].

From 1998, the potential of  $Si_3N_4$  as a gate dielectric was discovered and explored. The gate leakage current of JVD silicon nitride is significantly lower than that of silicon dioxide with the same equivalent oxide thickness, and the breakdown characteristics of JVD nitride also show good performance, and a higher dielectric constant. At the same time, it provides excellent coverage in field-effect transistors while maintaining its good carrier mobility [10, 11]. With the development of technology, researches on  $Si_3N_4$  have became more mature, the current technology can make good use of it chemistry has high directivity and high selectivity to Si and  $SiO_2$  [12], it might be a good substitute of  $SiO_2$  for gate dielectric.

High-k dielectric materials are one of the best choices to replace  $SiO_2$  [13], however, not all High-k dielectric materials are suitable, there are many other features that need to be considered its crystallinity and crystallographic phase, electrical properties such as band-gap, chemical stability at the interface and overall thermodynamic stability [14]. For example,  $Ta_2O_5$ ,  $TiO_2$  and STO are thermally unstable when in direct contact with Si [15]. In contrast, so they are not particularly suitable. A suitable high-k materials should ideally have a dielectric constant between 10-30 and a band-gap of 5eV and maintain a band offset of at least 1 eV with the silicon substrate, and for successful preparation, it needs to meet the requirements of 1000 K for at least 90 seconds [16].  $HfO_2$  is more stable with a high heat of formation, also, Hf can scav-enge native oxide to form HfO. What's more, the leakage current through a  $HfO_2$  gate oxide was several orders of magnitude lower than  $SiO_2$  at an operating voltage of 1-1.5 V [17].

## 2.2. High-k dielectric

**Table 1.** High-K Dielectric Permitivity.

| Material  | Dielectric Permittivity |

|-----------|-------------------------|

| SiO2      | 3.9                     |

| $Si_3N_4$ | 7                       |

| $HfO_2$   | 20-25                   |

For the Materials of Gate Insulator Layers, the dielectric constant (K) is a particularly important measurement standard, The FinFET is a capacitance-operated device, and the source-drain current of the FET is depend on the gate capacitance [18].

$$Cox = \frac{k\varepsilon A}{d} \tag{1}$$

$\epsilon$  is the relative permittivity of free space, and K is the dielectric constant, A is the area of cross-section, and d is the SiO<sub>2</sub> thickness.

For the same equivalent oxide layer thickness, high-k materials have a thicker physical thickness, which can effectively reduce gate leakage current [19].

Equivalent oxide layer thickness in high- k media:

$$t_{HK} = \frac{\varepsilon_{HK}}{\varepsilon_{OX}} \cdot t_{OX} \tag{2}$$

From equations (1) and (2), use high-k materials as the material of Gate Insulator Layers have many advantages.

Table 1 shows the dielectric constants of three materials. From the table, it can be seen that the dielectric constants of  $HfO_2$  and  $Si_3N_4$  are higher than those of  $SiO_2$ , and theoretically, they will have higher performance, and the performance of HF should be much higher than the other two [20].

# 3. Simulation and Comparison

#### 3.1. Model Parameters

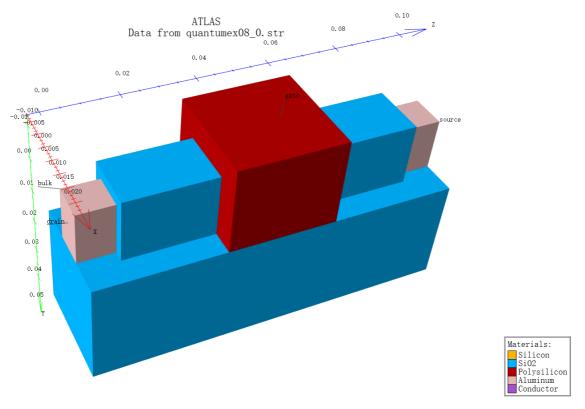

Figure 1. Quantum examples 3D FinFET model (Photo/Picture credit: Original).

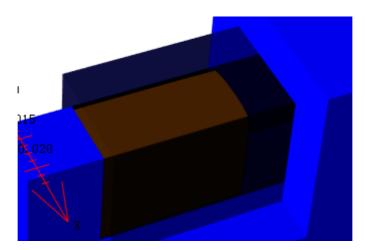

Figure 2. Gate insulator layers (Photo/Picture credit: Original).

The module is shown in Figure.1, it is the Quantum examples 3D FinFET model in Silvaco TCAD, this is a relatively standard 10nm FinFET model, its basic material composition is shown in the lower right corner of the figure, and in this module (default material structure), the material of gate insulator layers is SiO<sub>2</sub>. In Figure 2, the transparent brown part is the gate insulator layers which is defaulted to SiO<sub>2</sub>, and the material can be changed by modifying the code, including Si<sub>3</sub>N<sub>4</sub> and HfO<sub>2</sub>. After completing grid optimization and optimizing some output code, the program was been run, and finally output the structure diagram and IV curve diagram in TonyPlot (the roles and parameters of the x-axis and y-axis are determined by the optimized code). At last, the outputs of the three materials will be integrated on one coordinate axis.

# 3.2. Results of the ability to suppress leakage current

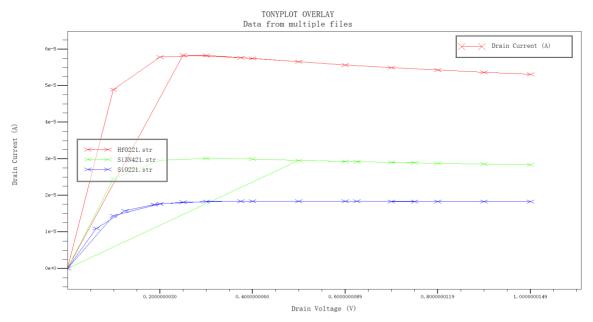

**Figure 3.** The result (Drain voltage and drain current) of TonyPlot (Photo/Picture credit: Original).

Through the figure 3 of Drain voltage and drain current, for  $SiO_2$ ,  $Si_3N_4$  and  $HfO_2$ , the module using  $HfO_2$  has the highest drain current threshold, and it is much higher than others, and the drain current threshold of the module using the  $Si_3N_4$  is also higher than the module using  $SiO_2$ .

# 3.3. Results of performance

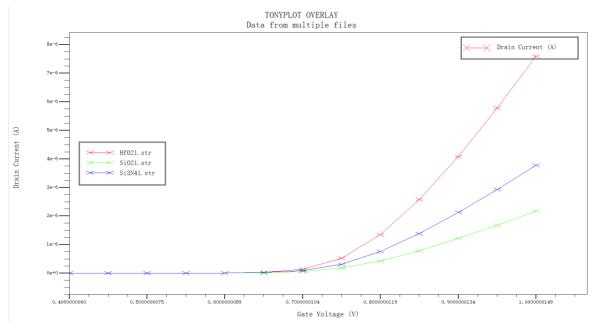

Figure 4. The result (Gate voltage and drain current) of TonyPlot (Photo/Picture credit: Original).

Through the figure 4 of Gate voltage and drain current, the region of Gate voltage is from 0.4 V to 1.0 V, the drain current of them (SiO2, Si<sub>3</sub>N<sub>4</sub> and HfO<sub>2</sub>) has a noticeable increase when the Gate voltage exceeds 0.7 V. It is easy to find that after the Gate voltage reaches 0.7 V, the drain current of HfO<sub>2</sub> is the highest at the same Gate voltage, and the drain current of Si<sub>3</sub>N<sub>4</sub> is also higher than the drain current of SiO2.

## 3.4. Comparison

In comparison, from the perspective of the ability to suppress leakage current, a high drain current threshold means before a significant leakage current occurs, the drain current can reach a higher value. Obviously, the ability to suppress leakage current of  $HfO_2$  is the best, and  $Si_3N_4$  also performs better than  $SiO_2$ .

And from the performance perspective, under the same voltage, the higher the current, the greater the power, and the better the performance, so the module using  $HfO_2$  has the highest performance, and the module using  $Si_3N_4$  also has better performance than the module using  $SiO_2$ .

Based solely on simulated data, comprehensive the ability to suppress leakage current and performance, both  $HfO_2$  and  $Si_3N_4$  can replace  $SiO_2$ , and  $HfO_2$  performs best in both aspects, so  $HfO_2$  would be a great substitute for  $SiO_2$ .

## 4. Challenges

For  $Si_3N_4$ , the manufacturing process of the material itself is relatively mature, and  $Si_3N_4$  has been widely used in many other fields. Its application in transistors is also constantly being optimized, and some manufacturers are now using  $Si_3N_4$  as the material of gate Insulator Layers. Even in GAAFET's model, the performance of  $Si_3N_4$  can completely replace that of SiO2 [20]. It may become the main material of gate Insulator Layers for the next few years.

For HfO<sub>2</sub>, in terms of manufacturing process, it still has many problems, whether in its own manufacturing or in its application to FinFET. Although it is significantly superior to the other two materials in various aspects of simulation data, if forcibly applied, it will not only incur high costs, but also face the problem of product yield. Anyway, HfO<sub>2</sub> has great potential, and this is why there has

always been research on HfO<sub>2</sub> and models have been established using HfO<sub>2</sub> as the material of gate Insulator Layers.

# 5. Conclusion

Simulation results indicate that  $HfO_2$  emerges as the prime candidate to supplant  $SiO_2$  in the role of gate insulator layers for FinFET applications. This conclusion aligns with  $HfO_2$ 's intrinsic properties that offer enhanced performance, particularly in the realm of FinFET technology. However, looking ahead and considering the trajectory of material advancements,  $Si_3N_4$  appears to be the front-runner for an eventual, comprehensive replacement of  $HfO_2$  in the gate insulator domain of FinFET. Its promising characteristics, coupled with ongoing research and development efforts, signify its potential for widespread adoption. Additionally, HF, though not a direct substitute, is showing significant promise. This compound is gaining momentum in research circles, suggesting it might play a pivotal role in the future of semiconductor technology. As material science continues to evolve, the dynamic interplay of these materials will undoubtedly catalyze further innovations, shaping the next chapters in the story of FinFET development and broader semiconductor advancements.

#### Reference

- [1] Zareiee, M. (2019). A new architecture of the dual gate transistor for the analog and digital applications. AEU International Journal of Electronics and Communications, 100, 114-118

- [2] Bousari, N. B., Anvarifard, M. K., & Haji-Nasiri, S. (2019). Improving the electrical characteristics of nanoscale triple-gate junctionless FinFET using gate oxide engineering. AEU International Journal of Electronics and Communications, 108, 226-234.

- [3] Mukherjee, A., & Nagaria, R. K. (2021). A Comparative Study of various High-K Dielectric Materials as Gate Oxide Layer on TG FinFET. 2021 2nd Global Conference for Advancement in Technology (GCAT).

- [4] Robertson, J. (2004). High dielectric constant oxides. European Physics Journal Applied Physics, 28, 265-291.

- [5] Justeena, A. N., Nirmal, D., & Gracia, D. (2017). Design and analysis of tunnel FET using high K dielectric materials. 2017 International Conference on Innovations in Electrical, Electronics, Instrumentation and Media Technology (ICEEIMT).

- [6] Chowdhury, T. A. (2023). Simulation Study of 50 nm Gate Length MOSFET Characteristics, No.6.

- [7] Gill, A., Madhu, C., & Kaur, P. (2015). Investigation of short channel effects in Bulk MOSFET and SOI FinFET at 20nm node technology.

- [8] Zhao, J. (2008). High K-metal gate and 45 nanometers.

- [9] Zhao, Y. (2004). Recent progress in high k gate dielectrics.

- [10] Ma, T.P. (1998). Making silicon nitride film a viable gate dielectric. IEEE Transactions on Electron Devices, 45(3).

- [11] Zhu, W., Neumayer, D., Perebeinos, V., & Avouris, P. (2010). Silicon Nitride Gate Dielectrics and Band Gap Engineering in Graphene Layers.

- [12] Bacquié, V., Tavernier, A., Boulard, F., Pollet, O., & Possémé, N. (2021). Gate spacers etching of Si3N4 using cyclic approach for 3D CMOS devices.

- [13] Kang, L., Qi, W-J. (1999). Highly Reliable Thin Hafnium Oxide Gate Dielectric.

- [14] Muralidharan, A. (2022). An Investigation into the HfO2/Si Interface: Materials Science Challenges and their Effects on MOSFET Device Performance.

- [15] Alers, G.B., Werder, D., Chabal, Y., & Urdahl, R. (1998). Intermixing at the tantalum oxide/silicon interface in gate dielectric structures.

- [16] Choi, J. H., Mao, Y., & Chang, J. P. (2011). Development of hafnium based high-k materials—a review. Materials Science and Engineering: R: Reports, 72(6), 97–136.

- [17] Robertson, J. (2004). High dielectric constant oxides. Eur. Phys. J. Appl. Phys., 28(3), 265–291.

- [18] Bousari, N. B., Anvarifard, M. K., & Haji-Nasiri, S. (2019). Improving the electrical characteristics of nanoscale triple-gate junctionless FinFET using gate oxide engineering. International Journal of Electronics and Communications (AEÜ), 108, 226-234.

- [19] Salmani-Jelodar, M., Ilatikhameneh, H., Kim, S., Sarangapani, P., & Klimeck, G. (2016). Optimum High-k Oxide for the Best Performance of Ultra-scaled Double-Gate MOSFETs.

- [20] Diebold, A. C., Antonelli, G. A., & Keller, N. (2018). Perspective: Optical measurement of feature dimensions and shapes by scatterometry.