1. Introduction

As a third-generation wide bandgap semiconductor device, the SiC MOSFET (Metal-Oxide-Semiconductor Field-Effect Transistor) is widely utilized in aerospace, rail transit, electric vehicles, new energy power generation, and other high-tech fields due to its advantages, including a wide bandgap, strong heat dissipation performance, fast switching speed, and high breakdown field strength [1,2].

However, in practical applications, SiC MOSFET devices encounter several issues that can lead to experimental failures or application obstacles, ultimately reducing the reliability of these new devices. This paper discusses and analyzes the problems encountered in SiC MOSFET applications, categorizing them as follows: The short-circuit issue arises because the internal chip area of a SiC MOSFET is much smaller than that of traditional Si material devices, causing the unit chip area to bear higher short-circuit currents and generate more heat. Without timely short-circuit protection, the SiC MOSFET may burn out [3]. The avalanche issue occurs when the SiC MOSFET operates at a voltage exceeding its specification or surpasses its maximum withstand voltage limit due to abnormal system conditions. This effect is more pronounced in SiC MOSFETs compared to Si devices because their high electric field strength accelerates carrier generation [4]. Switching oscillations refer to the strong current and voltage changes that can cause the device to mislead or mistakenly shut down, interacting with the parasitic parameters of the power circuit and resulting in severe switching oscillations. Such oscillations not only increase switching losses but also affect the stability of the entire system and, in severe cases, may damage both the device and the system [5-7]. The bridge-arm crosstalk problem occurs in most cases when SiC MOSFETs are used in bridge-arm rectifier inverters. Due to the high switching speed, even minimal stray parameters in the circuit can lead to crosstalk issues on the gate drive side of the SiC MOSFET adjacent to the same bridge arm [8,9].

In response to these problems, this paper explores basic solutions as follows: By using a Hall element to detect short-circuit current, measuring changes in the SiC MOSFET's drain-source voltage to assess short-circuit conditions, and employing Rogowski coil detection methods, the device's short-circuit resistance can be improved [10,11]. The avalanche effect can be mitigated by employing desaturation protection and multi-layer protection to promptly halt charge accumulation. Switching oscillations can be addressed at three levels: the SiC MOSFET switch control algorithm level, the drive power circuit level, and the main circuit power circuit level. Solutions include dead zone control, output distortion compensation, and soft switching at the control algorithm level. The bridge-arm crosstalk problem in SiC MOSFET devices is mainly suppressed by negative voltage turn-off suppression, passive suppression, and active suppression methods [12,13].

The structure of this paper is as follows: The first part is the introduction, the second part discusses the current problems associated with SiC MOSFETs, the third part analyzes methods for addressing these challenges, and the fourth part presents the conclusion.

2. Reliability Issues of SiC MOSFET

2.1. Short Circuit and Avalanche Problems

Short Circuit Problem of SiC MOSFET: Unlike traditional Si material devices, SiC MOSFETs, despite their significant advantages in high-temperature resistance, radiation resistance, and heat dissipation, have a much smaller internal chip area. This smaller chip area makes SiC MOSFETs bear more short-circuit current per unit area and generate more heat during a short-circuit fault [14]. If short-circuit protection is not implemented promptly, the SiC MOSFET can be destroyed. Designing a suitable protection and detection circuit for SiC MOSFETs is a prominent research topic [15].

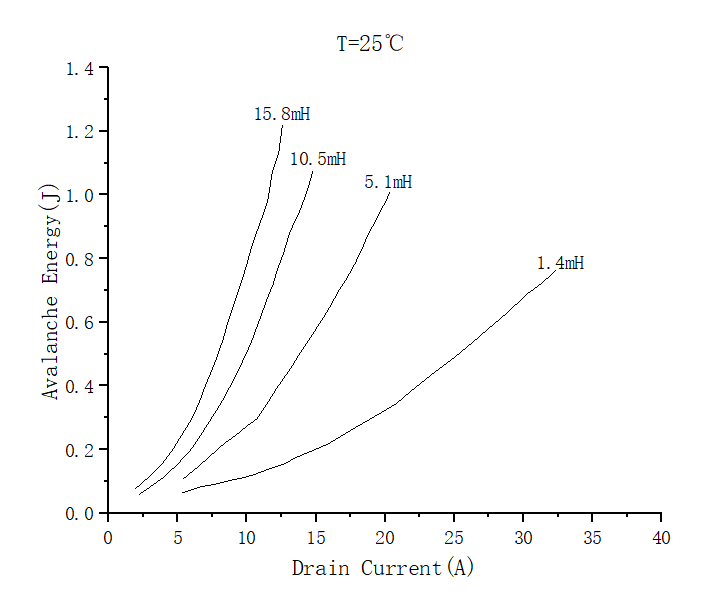

SiC MOSFET Avalanche Problem: Due to the characteristics of SiC materials, SiC MOSFETs are prone to avalanche phenomena when operating at high voltages, which can lead to device failure. The relationship between avalanche energy and drain current was measured at 25°C and 125°C, respectively. As shown in Figure 1, the comparison indicates that the smaller the inductance, the shorter the avalanche energy and duration, as generating sufficient avalanche energy requires a higher avalanche current. Conversely, the larger the inductance, the greater the avalanche energy. Compared to silicon devices, the avalanche capability of SiC MOSFETs is less sensitive to temperature. As the temperature increases, the duration and energy of avalanches decrease slightly [16].

Figure 1: The Relationship between Avalanche Energy and Drain Current [17].

The negative gate turn-off voltage positively affects the avalanche capability of SiC MOSFETs. A negative turn-off voltage of -5V slightly improves avalanche resistance compared to a zero turn-off gate voltage. This is primarily because a high negative gate turn-off voltage helps to keep the MOS channel off, causing the source current to take longer to pass through the channel.

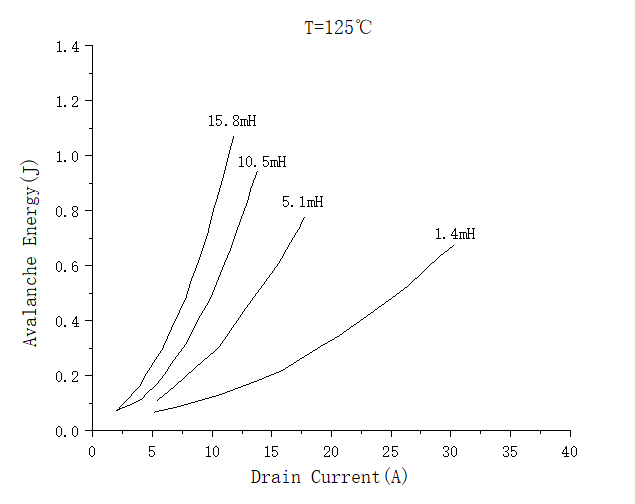

Under avalanche stress, the device experiences significant power loss due to the high drain voltage. Figure 2 shows the typical single-pulse waveform of a 1200V/36A SiC MOSFET under avalanche conditions. The voltage across the MOSFET reaches a peak of 1800V. The avalanche state lasts for 15 microseconds, during which the drain voltage first increases with the junction temperature and then decreases due to the low impact ionization rate at high temperature. Finally, the voltage between the drain and the source suddenly drops, forming a conductive path between the drain and the source, which results in a sharp increase in drain leakage current [18].

Figure 2: Avalanche Experiment Diagram [18].

2.2. Switch oscillation and bridge arm crosstalk problems

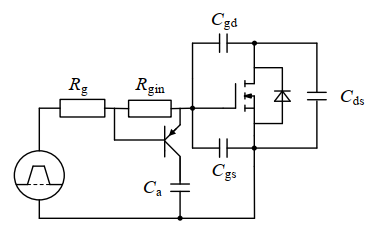

SiC MOSFET Switching Oscillation Problem: Due to the superior characteristics of SiC materials, SiC MOSFETs can operate at higher frequencies and voltages, leading to greater rates of current change (di/dt) and voltage change (dv/dt) when the MOSFETs are turned on and off. Strong changes in current and voltage can cause electromagnetic interference (EMC) in the control circuit, resulting in mis-conduction or unintentional shutdown of the device. These changes also interact with the parasitic parameters of the power loop, leading to severe switching oscillations. Severe switching oscillations not only increase switching losses but also impact the stability of the entire system. In extreme cases, they can cause damage to the device and even the entire system [19-21].

SiC MOSFET Bridge Arm Crosstalk Problem: In most cases, SiC MOSFETs are used in bridge-arm rectifier inverters. Due to the high-frequency switching speed, even very small stray parameters in the circuit can cause crosstalk issues on the gate drive side of the SiC MOSFET adjacent to the same bridge arm [22]. The gate voltage tolerance of SiC MOSFETs is limited; when the forward gate voltage exceeds 25V or the reverse voltage exceeds -10V, the SiC MOSFET may experience gate breakdown, ultimately leading to device failure [23]. Therefore, the crosstalk problem is a significant obstacle in the application of SiC MOSFETs in high-frequency fields, warranting further research and exploration by scholars.

3. Methods to Improve the Reliability of SiC MOSFET

3.1. Methods to Improve Short-Circuit and Avalanche Resistance

To enhance short-circuit resistance, some scholars have proposed using a Hall element to detect short-circuit currents by monitoring changes in the SiC MOSFET current. However, the Hall element suffers from low sensitivity, poor temperature characteristics, and susceptibility to electromagnetic interference. This detection scheme does not account for the protection response time nor confirm the accuracy of detection. Subsequently, the desaturation detection method was introduced, which determines short-circuit conditions by monitoring changes in the drain-source voltage of the SiC MOSFET. This method can be applied to both Si IGBT and SiC MOSFET detection and has a relatively simple structure, although it requires careful setting of the detection blind area. Another approach involves using the parasitic inductance within the SiC MOSFET power module to detect the device's operating state. The principle here is that changes in the SiC MOSFET current produce a voltage drop across the parasitic inductance, with the short-circuit condition identified by detecting this voltage drop [24]. Some Western scholars have developed a method using a PCB Rogowski coil to design a PCB Rogowski coil, which is placed on the source pin of the SiC MOSFET to detect short circuits by monitoring the source current. However, the PCB Rogowski coil occupies significant space, exhibits poor stability, and has weak anti-interference capabilities. This method requires further study. Other researchers have explored gate voltage detection methods, wherein the gate voltage changes when the SiC MOSFET experiences a short circuit, allowing the device's operating condition to be assessed by monitoring the gate voltage. However, this method involves a complex structure, cumbersome logic, and low stability. Based on the above analysis, the desaturation detection method is relatively simple and stable [25,26].

To improve avalanche resistance, two main methods are currently employed. The first is desaturation protection, which utilizes a driver with desaturation protection capabilities that can respond rapidly after a short circuit occurs, such as Power Integration's SCALE-2 IGBT gate driver. The second method is multi-layer protection, which combines various protection technologies, such as an integrated desaturation circuit driver, to enhance overall avalanche resistance [27].

3.2. Methods to Suppress Switching Oscillation and Bridge Arm Crosstalk

Regarding switching oscillation suppression, researchers globally have conducted in-depth studies on SiC MOSFET switching oscillations, employing various methods to analyze and address this issue from different perspectives. Early studies on SiC MOSFET switching oscillations were conducted through simulations, which demonstrated the influence of parasitic parameters on switching oscillations. However, these studies lacked experimental data support. In contrast, other scholars utilized Matlab to construct a mathematical model and combined it with experimental data to more comprehensively analyze the impact of parasitic parameters on switching oscillations. Some research teams have proposed that the drive circuit parameters influence the switching transients of SiC MOSFETs, supported by simulation and double-pulse experiments, providing valuable references for addressing switching oscillation issues. Additionally, research has extended to control algorithm and circuit design levels. Other scholars have focused on suppressing switching oscillations by optimizing control algorithms, drive power circuits, and main circuit power circuits [28,29]. Among these efforts, research on the control algorithm level successfully addresses the problem of bridge-arm shoot-through and output distortion by adjusting the dead time and compensating for output distortion. Another group of researchers effectively reduced oscillation amplitude and decreased over-voltage and over-current during switching transients by adding an RC snubber circuit to the main circuit. Simultaneously, scientists have introduced the application of soft-switching technology to alter the switching trajectory of SiC MOSFETs, significantly reducing switching losses and oscillations [30]. Further research indicates that high-frequency oscillations generated during the SiC MOSFET switching process can cause greater interference to the system control side, potentially leading to incorrect signal triggering or shutdown. Finally, some experts compared switching oscillation issues in power devices made of different materials and analyzed the influence of parasitic parameters in these devices [31-33].

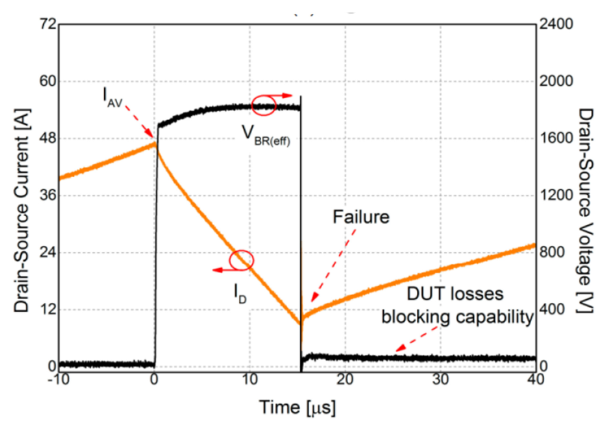

To resolve bridge-arm crosstalk, three main methods are commonly used. The negative voltage turn-off suppression method involves converting the driving turn-off voltage signal into a negative voltage to prevent the SiC MOSFET from being mis-triggered. Simulations and experimental analyses have shown that negative gate voltage can accelerate the turn-off speed of SiC MOSFETs and reduce losses. However, since the maximum negative voltage tolerance of SiC MOSFETs is -10V, while negative voltage turn-off effectively suppresses forward crosstalk, it increases the risk of reverse crosstalk. If the negative voltage value is not set appropriately, it may lead to negative voltage breakdown of the SiC MOSFET [34]. The passive suppression method reduces crosstalk by lowering the turn-on and turn-off speeds of the SiC MOSFET, which in turn decreases the current change rate (di/dt) and voltage change rate (dv/dt). By increasing the resistance of the drive circuit or the capacitance of the gate-source capacitance, the charging speed of the drive circuit to the gate-source capacitance is reduced, achieving the goal of lowering the turn-on and turn-off speeds of the SiC MOSFET. However, while this method suppresses switching oscillations, it also reduces switching speed and increases losses during the entire switching operation, potentially impacting its application in high-frequency fields [35-37]. Compared to the passive suppression method, the active suppression method is more flexible. Unlike the simple parallel gate-source capacitance method, active suppression has a relatively smaller impact on the switching speed of the SiC MOSFET [38].

Figure 3: Active Suppression Circuit [38].

4. Conclusion

In this paper, the short-circuit phenomenon, avalanche effect, switching oscillation phenomenon, and bridge-arm crosstalk in SiC MOSFETs have been studied. The generation and working mechanisms of common issues such as short circuits and avalanches have been analyzed in detail. Based on the characteristics of SiC MOSFETs, methods to enhance short-circuit and avalanche resistance, as well as to suppress switching oscillation and bridge-arm crosstalk, have been proposed. This research provides theoretical support for the application of SiC MOSFETs.

References

[1]. Wang J, Zhao T, Li J, et al.Characterization, Modeling, and Application of 10-kV SiC MOSFET[J].IEEE Transactions on Electron Devices, 2008, 55(8):1798-1806.DOI:10.1109/TED.2008.926650.

[2]. Wang J, Jiang X. Review and analysis of SiC MOSFETs’ ruggedness and reliability[J]. IET Power Electronics, 2020, 13(3): 445-455.

[3]. Reigosa P D, Iannuzzo F, Luo H, et al.A Short-Circuit Safe Operation Area Identification Criterion for SiC MOSFET Power Modules[J].IEEE Transactions on Industry Applications, 2017, 53(3):2880-2887.DOI:10.1109/TIA.2016.2628895.

[4]. Masuda T, Wada K, Hiyoshi T, et al.A Novel Truncated V-groove 4H-SiC MOSFET with High Avalanche Breakdown Voltage and Low Specific On-resistance[J].Materials Science Forum, 2014, 778-780:907-910.DOI:10.4028/www.scientific.net/MSF.778-780.907.

[5]. Zheng Chen, Dushan Boroyevich, Rolando Burgos. Experimental parametric study of the parasitic inductance influence on MOSFET switching characteristics[C]. International Power Electronics Conference 2010, Sapporo, Japan, 2010: 164-169.

[6]. Jianjing Wang, Henry Shu-hung Chung, River Tin-ho Li. Characterization and Experimental of the Effects of Parasitic Elements on the MOSFET Switching Performance[J]. IEEE Transactions on Power Electronics, 2013, 28(1): 573-590.

[7]. Jukkrit Noppakunkajorn, Di Han, Bulent Sarlioglu. Analysis of High-Speed PCB with SiC Devices by Investigating Turn-off Overvoltage and Interconnection Inductance Influence[J]. IEEE Transactions on Transportation Electrification, 2015, 1(2): 118-125.

[8]. Saeed Jahdi, Olayiwola Alatise, Jose Angel Ortiz, et al. Temperature and Switching Rate Dependence of Crosstalk in Si-IGBT and SiC Power Modules[J]. IEEE Transactions on Power Electronics, 2017, 32(5): 3355-3369.

[9]. Jianjing Wang, Henry Shu-Hung. Impact of Parisitic Elements on the Spurious Triggering Pulse in Synchronous Buck Converter[J]. IEEE Transactions on Power Electronics, 2014, 29(12): 6672-6685

[10]. Z. Wang et al. Temperature-Dependent Short-Circuit Capability of Silicon Carbide Power MOSFETs[J]. IEEE Transactions on Power Electronics, 2016, 31(2), 1555-1556.

[11]. Boige F, Richardeau F. Gate leakage-current analysis and modelling of planar and trench powerSiC MOSFET devices in extreme short-circuit operation[J]. Microelectronics Reliability, 2017, 76: 532-538.

[12]. Jacobs M E, Timm K J, Thottuvelil V J. Apparatus and method for generating negative bias for isolated mosfet gate-drive circuits[J]. EP, 1996, 14(3): 436-464.

[13]. Wang J, Chung H S H. A novel RCD level shifter for elimination of spurious turn-on in the bridge-leg configuration[J]. IEEE Trans on Power Electronics, 2015, 13(3): 976-984.

[14]. Cao W, Yin S, Ge X, et al.SiC superjunction MOSFET with Schottky diode for improving short-circuit and reverse recovery ruggedness[J].Micro and Nanostructures, 2024, 191.DOI:10.1016/j.micrna.2024.207847.

[15]. Wang Z, Tong C, Huang W. Short-circuit protection method for medium-voltage SiC MOSFET based on gate-source voltage detection[J]. Journal of power electronics: A publications of the Korean Institute of Power Electronics, 2020(4):20.DOI:10.1007/s43236-020-00095-7.

[16]. Chen D X, Wang Y, Song Y X, et al.SiC Super-Junction MOSFET robustness assessment and method to improve avalanche capability[J].Microelectronics Reliability, 2024, 157.DOI:10.1016/j.microrel.2024.115418.

[17]. Kelley, M.D., Pushpakaran, B.N., Bayne, S.B.: 'Single-pulse avalanche mode robustness of commercial 1200 V/80 mΩ SiC MOSFETs’, IEEE Trans. Power Electron., 2017, 32, (8), pp. 6405–6415

[18]. Fayyaz, A., Romano, G., Urresti, J., et al.: ‘A comprehensive study on the avalanche breakdown robustness of silicon carbide power MOSFETs’,Energies, 2017, 10, pp. 1–15

[19]. Zheng Chen, Dushan Boroyevich, Rolando Burgos. Experimental parametric study of the parasitic inductance influence on MOSFET switching characteristics[C]. International Power Electronics Conference 2010, Sapporo, Japan, 2010: 164-169.

[20]. Jianjing Wang, Henry Shu-hung Chung, River Tin-ho Li. Characterization and Experimental of the Effects of Parasitic Elements on the MOSFET Switching Performance[J]. IEEE Transactions on Power Electronics, 2013, 28(1): 573-590.

[21]. Jukkrit Noppakunkajorn, Di Han, Bulent Sarlioglu. Analysis of High-Speed PCB with SiC Devices by Investigating Turn-off Overvoltage and Interconnection Inductance Influence[J]. IEEE Transactions on Transportation Electrification, 2015, 1(2): 118-125

[22]. Saeed Jahdi, Olayiwola Alatise, Jose Angel Ortiz, et al. Temperature and Switching Rate Dependence of Crosstalk in Si-IGBT and SiC Power Modules[J]. IEEE Transactions on Power Electronics, 2017, 32(5): 3355-3369.

[23]. Jianjing Wang, Henry Shu-Hung. Impact of Parisitic Elements on the Spurious Triggering Pulse in Synchronous Buck Converter[J]. IEEE Transactions on Power Electronics, 2014, 29(12): 6672-6685

[24]. Ilves,Kalle,Nawaz,et al.On the short-circuit and avalanche ruggedness reliability assessment of SiC MOSFET modules[J].Microelectronics and reliability, 2017, 71(Apr.):6-16.

[25]. Du H, Reigosa P D, Iannuzzo F, et al.Investigation on the degradation indicators of short-circuit tests in 1.2kV SiC MOSFET power modules[J].Pergamon Press, 2018.DOI:10.1016/j.microrel.2018.06.039.

[26]. Fisal A K. SHORT-CIRCUIT PROTECTION CIRCUIT FOR SWITCHING DEVICES FOR SIC OR GAN MOSFET TRANSISTOR AND ASSOCIATED METHOD: EP20180181938[P]. EP3425801A1[2024-09-01].

[27]. Fei H, Liang L, Zhang Z. Investigation on temperature limitation and failure mechanism of SiC MOSFETs under avalanche conditions[J]. Microelectronics and reliability, 2023, 150(Nov.):1.1-1.7.

[28]. Lewicki A. Dead-time effect compensation based on additional phase current measurements[J]. IEEE Transactions on Industrial Electronics, 2015, 62(7): 4078-4085.

[29]. Zhang Z, Wang F, Costinett D J, et al. Dead-time optimization of SiC devices for voltage source converter[C]. IEEE Applied Power Electronics Conference and Exposition (APEC), 2015: 1145-1152

[30]. Hua G, Lee F C. Soft-switching techniques in PWM converters[J]. IEEE Transactions on Industrial Electronics, 1995, 42(6): 595-603

[31]. Hao Chen, Deepak Divan. High speed switching issues of high power rated silicon-carbide devices and the mitigation methods[C]. 2015 IEEE Energy Conversion Congress and Exposition (ECCE), 2015: 2254-2260.

[32]. Shan Yin, K. J. Tseng, Pengfei Tu, et al. Design considerations and comparison of high-speed gate drivers for Si IGBT and SiC MOSFET modules[C]. 2016 IEEE Energy Conversion Congress and Exposition (ECCE), 2016: 1-8.

[33]. Muhamrnad Nawaz, Filippo Chimento, Kalle Ilves. Static and dynamic performance assessment of commercial SiC MOSFET power modules[C]. 2015 IEEE Energy Conversion Congress and Exposition (ECCE), 2015: 4899-4906.

[34]. Zhang Z, Wang F, Tolbert L M, et al. Active Gate Driver for Crosstalk Suppression of SiC Devices in a Phase-Leg Configuration[J]. IEEE Transactions on Power Electronics, 2013, 29(4): 1986-1997.

[35]. Zhang L, Guo S, Liu P, et al. Comparative Evaluation and Analysis of Gate Driver Impacts on a SiC MOSFET-Gate Driver Integrated Power Module[J]. International Symposium on Microelectronics, 2017, 2017(1): 000247-000251.

[36]. Stalter O, Burger B, Lehrmann S. Silicon Carbide (SiC) D-MOS for grid-feeding solarinverters[C]. IEEE 2007 European Conference on Power Electronics and Applications, Aalborg, 2007: 1-10.

[37]. Li G, Tong A, Hang L, et al. A Level Shift Gate Driving Circuit of SiC MOSFET with Crosstalk Suppression Capability[C]. 2020 IEEE Applied Power Electronics Conference and Exposition (APEC). IEEE, 2020.

[38]. Zhou Q. A Novel SiC MOSFET Gate Driver Circuit for Bridge Circuit[J]. Power Electronics, 2018, 33(4): 547-571.

Cite this article

Wang,Y. (2025). Research on the Reliability of SiC MOSFET Devices. Applied and Computational Engineering,126,46-52.

Data availability

The datasets used and/or analyzed during the current study will be available from the authors upon reasonable request.

Disclaimer/Publisher's Note

The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of EWA Publishing and/or the editor(s). EWA Publishing and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content.

About volume

Volume title: Proceedings of the 5th International Conference on Materials Chemistry and Environmental Engineering

© 2024 by the author(s). Licensee EWA Publishing, Oxford, UK. This article is an open access article distributed under the terms and

conditions of the Creative Commons Attribution (CC BY) license. Authors who

publish this series agree to the following terms:

1. Authors retain copyright and grant the series right of first publication with the work simultaneously licensed under a Creative Commons

Attribution License that allows others to share the work with an acknowledgment of the work's authorship and initial publication in this

series.

2. Authors are able to enter into separate, additional contractual arrangements for the non-exclusive distribution of the series's published

version of the work (e.g., post it to an institutional repository or publish it in a book), with an acknowledgment of its initial

publication in this series.

3. Authors are permitted and encouraged to post their work online (e.g., in institutional repositories or on their website) prior to and

during the submission process, as it can lead to productive exchanges, as well as earlier and greater citation of published work (See

Open access policy for details).

References

[1]. Wang J, Zhao T, Li J, et al.Characterization, Modeling, and Application of 10-kV SiC MOSFET[J].IEEE Transactions on Electron Devices, 2008, 55(8):1798-1806.DOI:10.1109/TED.2008.926650.

[2]. Wang J, Jiang X. Review and analysis of SiC MOSFETs’ ruggedness and reliability[J]. IET Power Electronics, 2020, 13(3): 445-455.

[3]. Reigosa P D, Iannuzzo F, Luo H, et al.A Short-Circuit Safe Operation Area Identification Criterion for SiC MOSFET Power Modules[J].IEEE Transactions on Industry Applications, 2017, 53(3):2880-2887.DOI:10.1109/TIA.2016.2628895.

[4]. Masuda T, Wada K, Hiyoshi T, et al.A Novel Truncated V-groove 4H-SiC MOSFET with High Avalanche Breakdown Voltage and Low Specific On-resistance[J].Materials Science Forum, 2014, 778-780:907-910.DOI:10.4028/www.scientific.net/MSF.778-780.907.

[5]. Zheng Chen, Dushan Boroyevich, Rolando Burgos. Experimental parametric study of the parasitic inductance influence on MOSFET switching characteristics[C]. International Power Electronics Conference 2010, Sapporo, Japan, 2010: 164-169.

[6]. Jianjing Wang, Henry Shu-hung Chung, River Tin-ho Li. Characterization and Experimental of the Effects of Parasitic Elements on the MOSFET Switching Performance[J]. IEEE Transactions on Power Electronics, 2013, 28(1): 573-590.

[7]. Jukkrit Noppakunkajorn, Di Han, Bulent Sarlioglu. Analysis of High-Speed PCB with SiC Devices by Investigating Turn-off Overvoltage and Interconnection Inductance Influence[J]. IEEE Transactions on Transportation Electrification, 2015, 1(2): 118-125.

[8]. Saeed Jahdi, Olayiwola Alatise, Jose Angel Ortiz, et al. Temperature and Switching Rate Dependence of Crosstalk in Si-IGBT and SiC Power Modules[J]. IEEE Transactions on Power Electronics, 2017, 32(5): 3355-3369.

[9]. Jianjing Wang, Henry Shu-Hung. Impact of Parisitic Elements on the Spurious Triggering Pulse in Synchronous Buck Converter[J]. IEEE Transactions on Power Electronics, 2014, 29(12): 6672-6685

[10]. Z. Wang et al. Temperature-Dependent Short-Circuit Capability of Silicon Carbide Power MOSFETs[J]. IEEE Transactions on Power Electronics, 2016, 31(2), 1555-1556.

[11]. Boige F, Richardeau F. Gate leakage-current analysis and modelling of planar and trench powerSiC MOSFET devices in extreme short-circuit operation[J]. Microelectronics Reliability, 2017, 76: 532-538.

[12]. Jacobs M E, Timm K J, Thottuvelil V J. Apparatus and method for generating negative bias for isolated mosfet gate-drive circuits[J]. EP, 1996, 14(3): 436-464.

[13]. Wang J, Chung H S H. A novel RCD level shifter for elimination of spurious turn-on in the bridge-leg configuration[J]. IEEE Trans on Power Electronics, 2015, 13(3): 976-984.

[14]. Cao W, Yin S, Ge X, et al.SiC superjunction MOSFET with Schottky diode for improving short-circuit and reverse recovery ruggedness[J].Micro and Nanostructures, 2024, 191.DOI:10.1016/j.micrna.2024.207847.

[15]. Wang Z, Tong C, Huang W. Short-circuit protection method for medium-voltage SiC MOSFET based on gate-source voltage detection[J]. Journal of power electronics: A publications of the Korean Institute of Power Electronics, 2020(4):20.DOI:10.1007/s43236-020-00095-7.

[16]. Chen D X, Wang Y, Song Y X, et al.SiC Super-Junction MOSFET robustness assessment and method to improve avalanche capability[J].Microelectronics Reliability, 2024, 157.DOI:10.1016/j.microrel.2024.115418.

[17]. Kelley, M.D., Pushpakaran, B.N., Bayne, S.B.: 'Single-pulse avalanche mode robustness of commercial 1200 V/80 mΩ SiC MOSFETs’, IEEE Trans. Power Electron., 2017, 32, (8), pp. 6405–6415

[18]. Fayyaz, A., Romano, G., Urresti, J., et al.: ‘A comprehensive study on the avalanche breakdown robustness of silicon carbide power MOSFETs’,Energies, 2017, 10, pp. 1–15

[19]. Zheng Chen, Dushan Boroyevich, Rolando Burgos. Experimental parametric study of the parasitic inductance influence on MOSFET switching characteristics[C]. International Power Electronics Conference 2010, Sapporo, Japan, 2010: 164-169.

[20]. Jianjing Wang, Henry Shu-hung Chung, River Tin-ho Li. Characterization and Experimental of the Effects of Parasitic Elements on the MOSFET Switching Performance[J]. IEEE Transactions on Power Electronics, 2013, 28(1): 573-590.

[21]. Jukkrit Noppakunkajorn, Di Han, Bulent Sarlioglu. Analysis of High-Speed PCB with SiC Devices by Investigating Turn-off Overvoltage and Interconnection Inductance Influence[J]. IEEE Transactions on Transportation Electrification, 2015, 1(2): 118-125

[22]. Saeed Jahdi, Olayiwola Alatise, Jose Angel Ortiz, et al. Temperature and Switching Rate Dependence of Crosstalk in Si-IGBT and SiC Power Modules[J]. IEEE Transactions on Power Electronics, 2017, 32(5): 3355-3369.

[23]. Jianjing Wang, Henry Shu-Hung. Impact of Parisitic Elements on the Spurious Triggering Pulse in Synchronous Buck Converter[J]. IEEE Transactions on Power Electronics, 2014, 29(12): 6672-6685

[24]. Ilves,Kalle,Nawaz,et al.On the short-circuit and avalanche ruggedness reliability assessment of SiC MOSFET modules[J].Microelectronics and reliability, 2017, 71(Apr.):6-16.

[25]. Du H, Reigosa P D, Iannuzzo F, et al.Investigation on the degradation indicators of short-circuit tests in 1.2kV SiC MOSFET power modules[J].Pergamon Press, 2018.DOI:10.1016/j.microrel.2018.06.039.

[26]. Fisal A K. SHORT-CIRCUIT PROTECTION CIRCUIT FOR SWITCHING DEVICES FOR SIC OR GAN MOSFET TRANSISTOR AND ASSOCIATED METHOD: EP20180181938[P]. EP3425801A1[2024-09-01].

[27]. Fei H, Liang L, Zhang Z. Investigation on temperature limitation and failure mechanism of SiC MOSFETs under avalanche conditions[J]. Microelectronics and reliability, 2023, 150(Nov.):1.1-1.7.

[28]. Lewicki A. Dead-time effect compensation based on additional phase current measurements[J]. IEEE Transactions on Industrial Electronics, 2015, 62(7): 4078-4085.

[29]. Zhang Z, Wang F, Costinett D J, et al. Dead-time optimization of SiC devices for voltage source converter[C]. IEEE Applied Power Electronics Conference and Exposition (APEC), 2015: 1145-1152

[30]. Hua G, Lee F C. Soft-switching techniques in PWM converters[J]. IEEE Transactions on Industrial Electronics, 1995, 42(6): 595-603

[31]. Hao Chen, Deepak Divan. High speed switching issues of high power rated silicon-carbide devices and the mitigation methods[C]. 2015 IEEE Energy Conversion Congress and Exposition (ECCE), 2015: 2254-2260.

[32]. Shan Yin, K. J. Tseng, Pengfei Tu, et al. Design considerations and comparison of high-speed gate drivers for Si IGBT and SiC MOSFET modules[C]. 2016 IEEE Energy Conversion Congress and Exposition (ECCE), 2016: 1-8.

[33]. Muhamrnad Nawaz, Filippo Chimento, Kalle Ilves. Static and dynamic performance assessment of commercial SiC MOSFET power modules[C]. 2015 IEEE Energy Conversion Congress and Exposition (ECCE), 2015: 4899-4906.

[34]. Zhang Z, Wang F, Tolbert L M, et al. Active Gate Driver for Crosstalk Suppression of SiC Devices in a Phase-Leg Configuration[J]. IEEE Transactions on Power Electronics, 2013, 29(4): 1986-1997.

[35]. Zhang L, Guo S, Liu P, et al. Comparative Evaluation and Analysis of Gate Driver Impacts on a SiC MOSFET-Gate Driver Integrated Power Module[J]. International Symposium on Microelectronics, 2017, 2017(1): 000247-000251.

[36]. Stalter O, Burger B, Lehrmann S. Silicon Carbide (SiC) D-MOS for grid-feeding solarinverters[C]. IEEE 2007 European Conference on Power Electronics and Applications, Aalborg, 2007: 1-10.

[37]. Li G, Tong A, Hang L, et al. A Level Shift Gate Driving Circuit of SiC MOSFET with Crosstalk Suppression Capability[C]. 2020 IEEE Applied Power Electronics Conference and Exposition (APEC). IEEE, 2020.

[38]. Zhou Q. A Novel SiC MOSFET Gate Driver Circuit for Bridge Circuit[J]. Power Electronics, 2018, 33(4): 547-571.