1. Introduction

With the ongoing advancement of semiconductor technology, the growing complexity of hardware and the delays caused by interconnections have become major challenges to the performance of System-on-Chip (SoC) designs. To address these challenges and enhance data transfer efficiency, the Network-on-Chip (NoC) architecture has emerged as a scalable, flexible, and reusable solution for chip multiprocessor (CMP) systems. NoC is a communication subsystem within an integrated circuit (IC) that enables data exchange between components like processors, memory units, and peripheral devices. As process technologies evolve and more cores are integrated into a single chip, the existing bus-based communication methods will no longer suffice. NoC is widely regarded as an optimal approach for developing modular and scalable communication architectures, with built-in support for integrating various core types by standardizing network interfaces [1]. Nowadays, more studies focus on the routing algorithm of NoCs due to the importance of finding the optimal one. Here are some of the reasons:

- Enhancing Performance and Minimizing Latency: Efficient routing algorithms are essential in minimizing the time for data packets to traverse the entire chip by selecting the shortest or fastest available paths. By effectively distributing the load across various pathways, superior routing algorithms prevent bottlenecks and ensure optimal data throughput.

- Energy efficiency: Optimal routing reduces the number of hops and avoids congested paths, thereby minimizing power consumption. This is particularly critical for battery-operated and low-power devices. Furthermore, efficient routing can facilitate a more uniform distribution of power dissipation across the chip, aiding in thermal management.

- Scalability: As the number of cores or IP blocks increases, it is imperative for the routing algorithm to scale effectively to manage more intricate communication patterns without compromising performance. The implementation of scalable routing algorithms ensures that the NoC is capable of accommodating future enhancements and a higher core count.

As a result, finding an optimal routing algorithm has led to heated discussion and has become a research focus. Our paper compares different adaptive routing algorithms regarding several aspects. Our paper started with Neighbor-on-Path (NoP) selection, then compared this with two other routing algorithms which both made progress by overcoming the disadvantages of NoP selection. Regional ant colony optimization-based cascaded adaptive routing (RACO-CAR) and holistic routing algorithm, a destination-based selection (DBSS) strategy, are described in depth in the following passage. These two schemes will be published later than the NoP method, and all advanced NoP selections will be in various fields.

2. Background

2.1. NoC Architecture

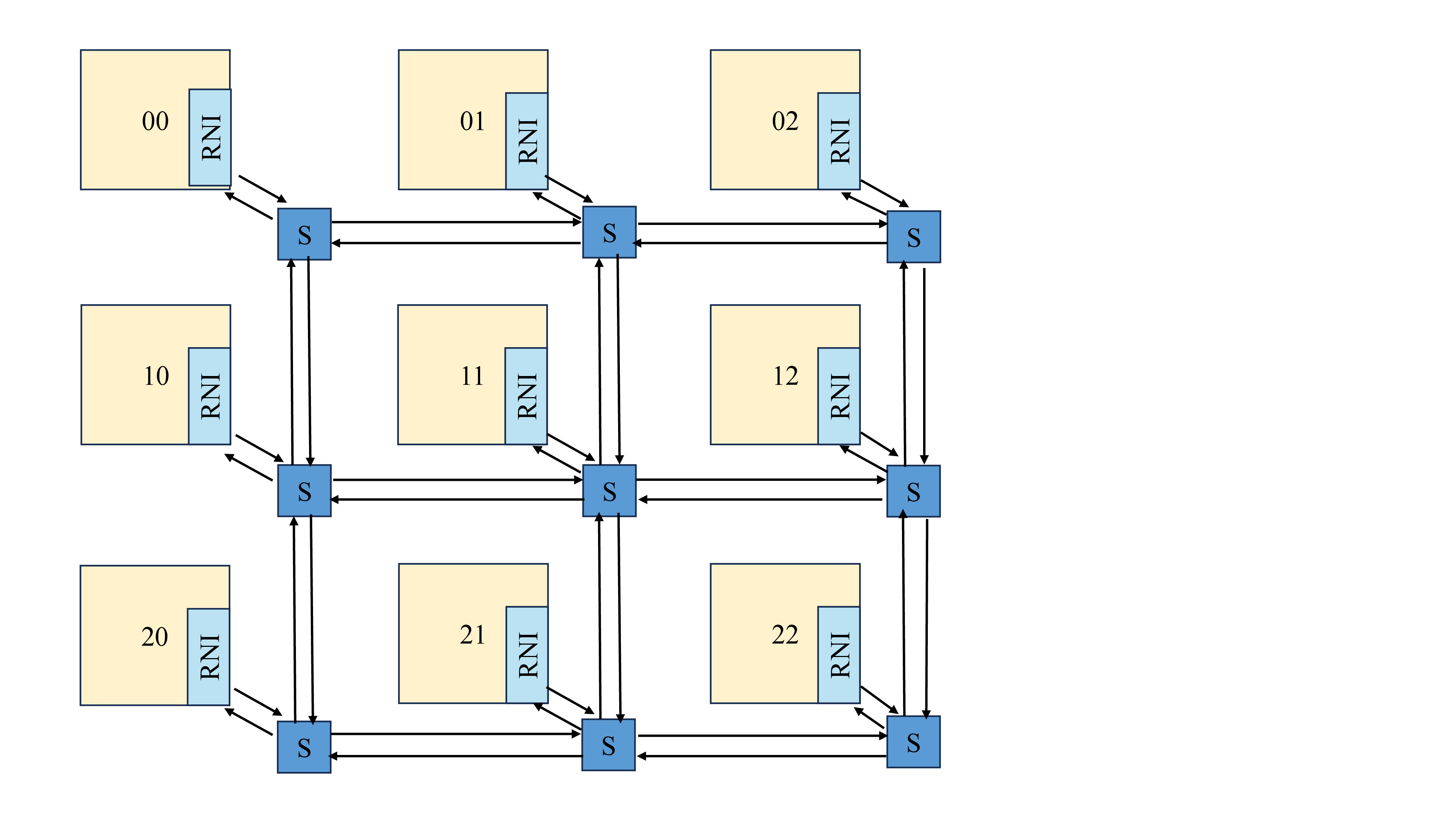

The NoC technology applies computer networking theory and methods to on-chip communication, resulting in significant improvements over traditional bus communication architectures, and is available in various network topologies . Most NoC architecture is now built on 2D-Mesh topology, as shown in Figure 1.

After reaching an intermediate node, a switching method helps to combine the input and output and form channels to set the switch. There are three widely recognized switching techniques: store-and-forward, virtual cut-through, and wormhole.

- Store-and-Forward Switching: In this method, the complete data frame is received and stored in a buffer before being sent to the destination. The switch verifies the frame for errors before forwarding it onward.

- Virtual Cut-Through Switching: In this method, the switch starts sending the data once the destination address are confined and enough of the message has been buffered to make a forwarding decision. However, there is a risk of forwarding corrupt or incomplete data if errors occur after the forwarding process has started.

- Wormhole Switching: Wormhole switching is a technique that combines aspects of both store-and-forward and cut-through switching. In wormhole switching, a small portion of the packet, known as a "worm," is initially stored and used to establish a path through the network. Once this path is set up, the data can start to flow through it before the entire packet has been received.

2.2. NoC Routing Algorithm

There are three main types of routing algorithms for NoC:

- Deterministic routing algorithm: These algorithms consistently give the same solution for a certain source and destination, such as XY routing and odd-even routing.

- Adaptive routing algorithm: These algorithms can choose different paths based on network conditions such as congestion or faults (west-first routing, minimal adaptive routing, etc.).

- Oblivious routing algorithm: These algorithms do not adapt to network conditions and follow pre-determined paths (Valiant's randomized routing etc.).

While considering choosing an optimal routing algorithm, we usually focus on aspects, such as deadlock and livelock avoidance, fault tolerance, scalability, power efficiency, etc. In our study, we concentrate on three types of adaptive routing algorithms specifically designed to dynamically adjust the path of data packets within a network based on current conditions such as congestion, faults, or traffic patterns. Through continuous monitoring of network conditions and real-time routing decisions, these algorithms play a crucial role in ensuring efficient, reliable, and fault-tolerant transmission. An adaptive routing algorithm comprises two components as shown in Figure 2: the routing function and the selection strategy [2]. The current addresses and information are imported into the main routing function, as it calculates the number of potential output routes. Then, the selection strategy chooses one route throughout all the possibilities according to the network's current status to form a final output that turns out to be the most ideal [3].

.png)

3. A New Method Relied on Adjacent Nodes in NoC

We review Neighbor-on-Path (NoP)[4] , combined with the Selection Function [5].

3.1. Analysis of NoP

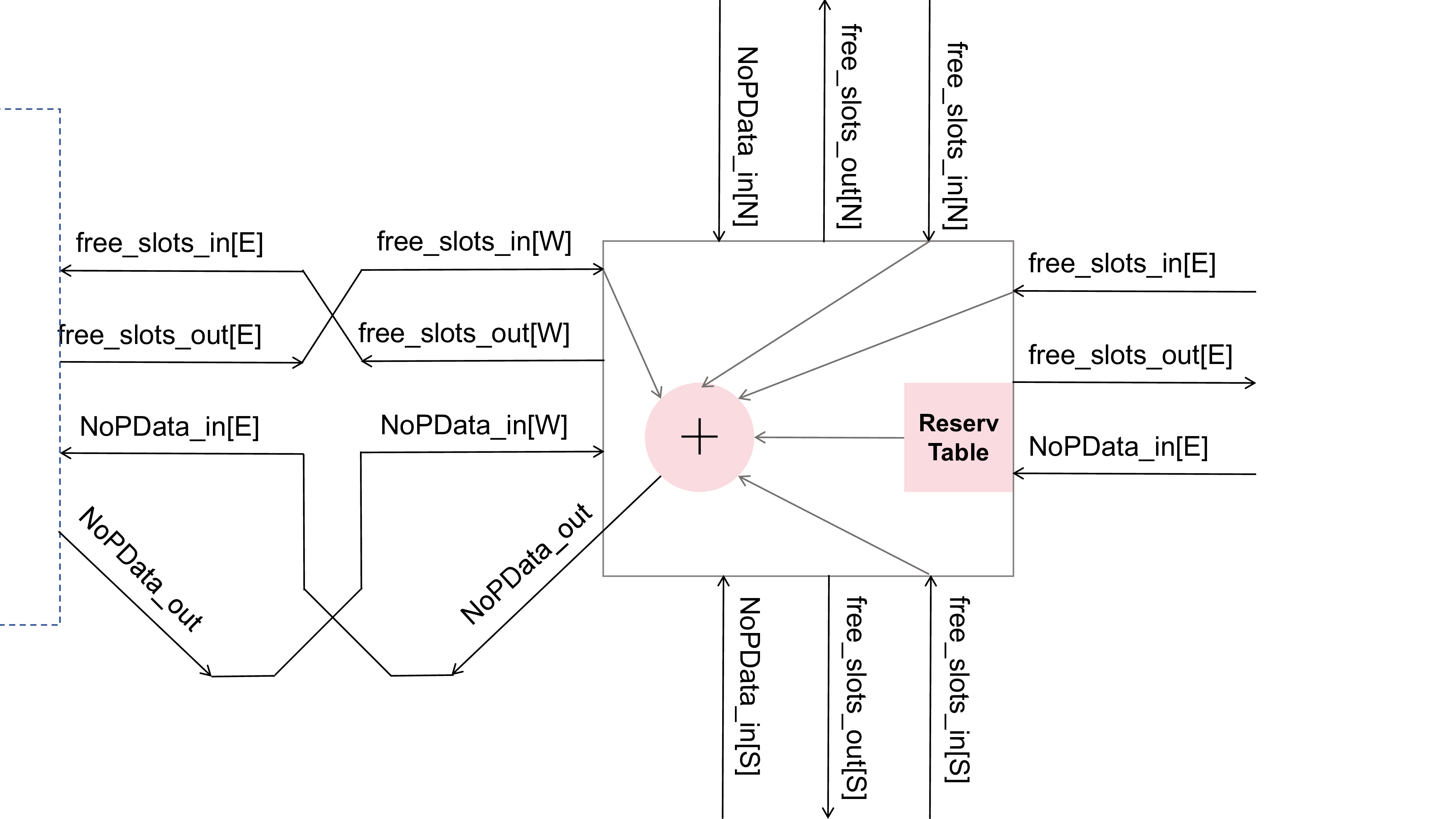

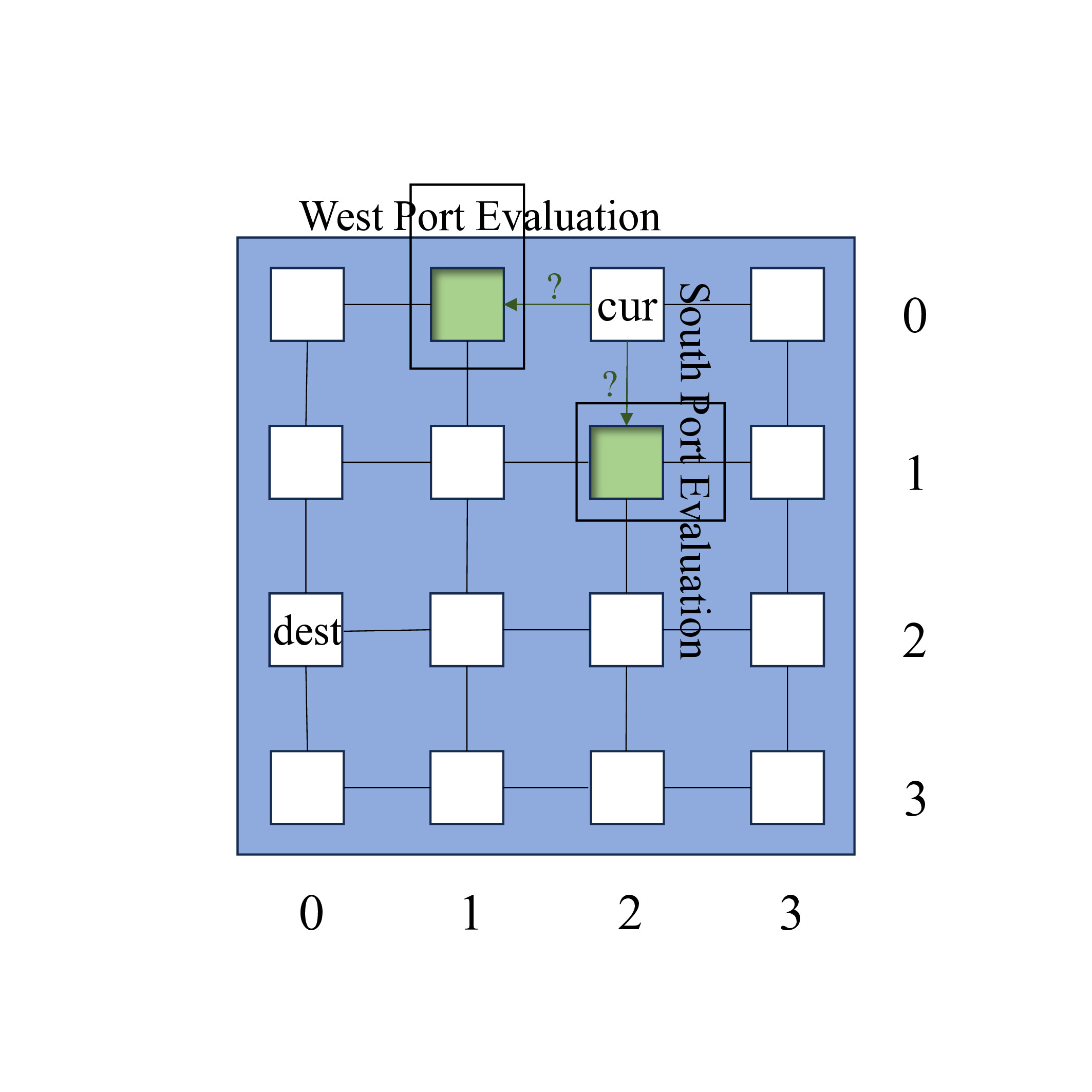

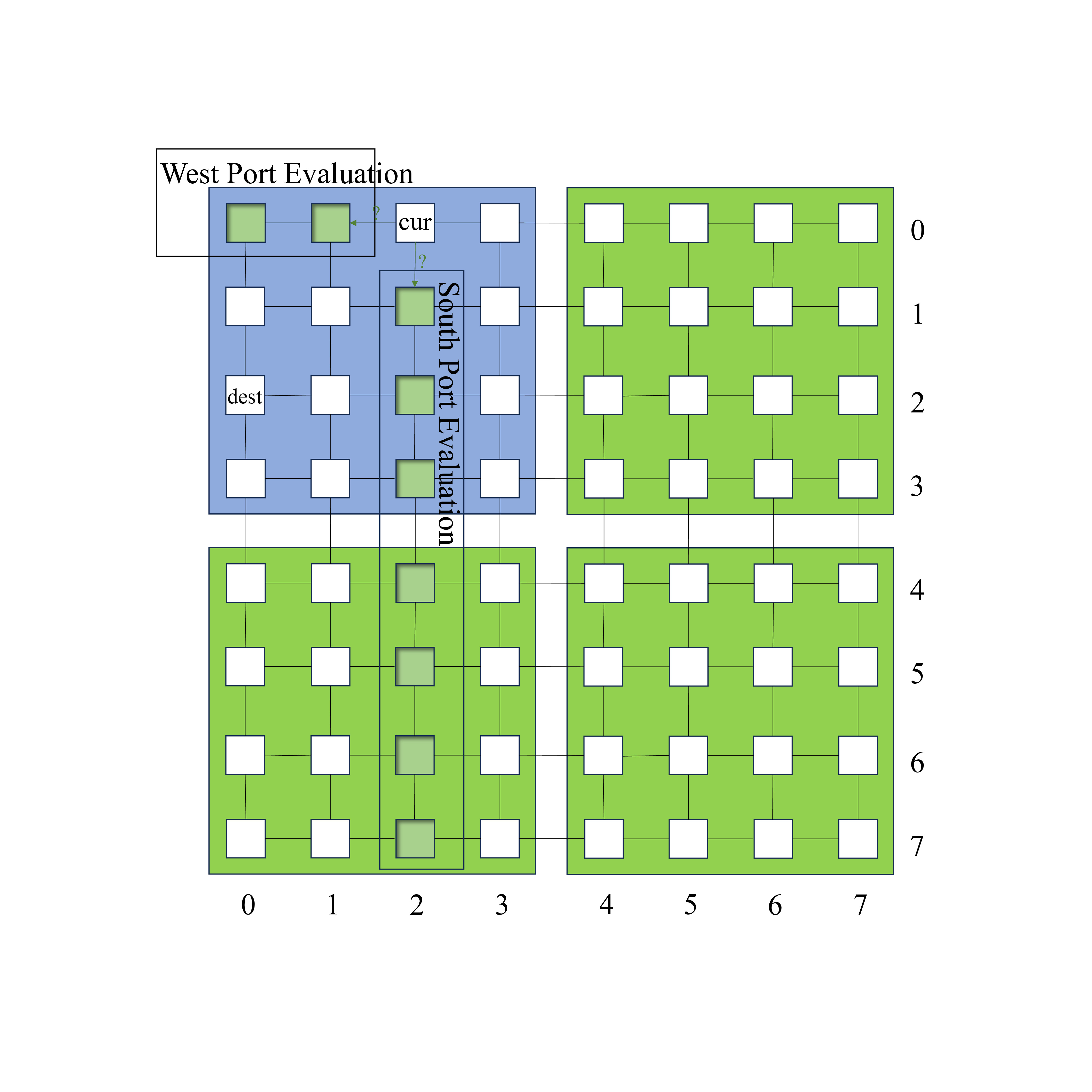

N is the number of nodes in a network, C is the communication channels, and PWC represents the power set of C. The adaptive routing feature offers a group of alternate output channels. All flits within the data packet should be directed to these channels, as illustrated below: \[ N \times N\rightarrow PWC \] To describe the NoP algorithm formally, they define some specific signals between two adjacent nodes and some parameters, referring to Figure 3. They are defined as follows:

- free\_slots\_in[d]: number of available free buffer slots for the adjacent node inputting in the direction d;

- free\_slots\_out[d]: number of available free buffer slots for current node inputting in the direction d;

- NoPData\_in[d]: NoP-specific scores calculated by neighbor nodes in the direction d;

- NoPData\_out[d]: NoP-specific scores for the current node by collecting input status information from adjacent nodes.

Two pieces of the pseudocode of the Neighbor-on-Path which illustrates how the selection algorithm is implemented are shown below in algorithm [???] and algorithm [???]. Please take note of the following text:

The algorithm collects information for adjacent neighbors from four directions, including free\_slots and available (line 1). The value of NoPData\_out[d].free\_slot is obtained from free\_slots\_in[d]. It gives the number of accessible free buffer slots in the direction d (line 2). NoPData\_out.available[d] is a Boolean function. If its value is "0", it represents the channel along the direction d is not reserved. On the contrary, if its value is "1", it represents the channel along the direction d is reserved (line 3). The local reservation table of the current router includes this value.

AOC is a set of available output channels that represents the input parameter. \(n_{c\lt /em\gt \) } is the current node and \(n_{d\lt /em\gt \) } is the destination node whose head flit must be routed. AOC is given by the function R:

\[ AOC=R(n_{c},n_{d})\]

Each output channel (line 2) is checked by calculating how many NoP nodes are available (lines 3-4). After this, candidate channels are identified and confirm whether their input buffer is practical.

Algorithm [???] uses a scoring mechanism to evaluate the available channels at node \(n_{c\lt /em\gt \) }. dest(ch) is used to represent the target node starting from the channel ch. A scoring mechanism is implemented to select the candidate destinations with the highest score when there is space in the non-reserved input buffer (lines 6-8). If multiple channels are all maximum scores, then select randomly. That is how the best channel is selected. What should be mentioned is that there is no need to put data exchanges into global synchronizing. And what is glad to see is that data needs to be updated consistently and regularly.

\caption{ComputeNoPData}

\begin{algorithmic}

\REQUIRE \(free\_slots\_in[]0\)

\ENSURE \(NoPData\_out\)

\FOR{ \(d \in \{North, South, East, West\}\) }

\STATE \(NoPData\_out[d].free\_slots arrow free\_slots\_in[d]\)

\STATE \(NoPData\_out[d].available arrow reservation\_table[d]\)

\ENDFOR

\end{algorithmic}

\caption{NoP\_Select}

\begin{algorithmic}

\REQUIRE \(AOC\)

\ENSURE \(sc\)

\STATE \(scores[] arrow 0\)

\FOR{ \(ch1 \in AOC\) }

\STATE \(node1 arrow dest(ch1)\)

\STATE \(AOC\_neighbor arrow R(node1, nd)\)

\FOR{ \(ch2 \in AOC\_neighbor\) }

\IF{ \(NoPData\_in[ch1].available[ch2]\) }

\STATE \(score[ch1] += NoPData\_in[ch1].free\_slots[ch2]\)

\ENDIF

\ENDFOR

\ENDFOR

\STATE \(sc arrow ch\) s.t. \(score[ch] = max(scores[])\)

\end{algorithmic}

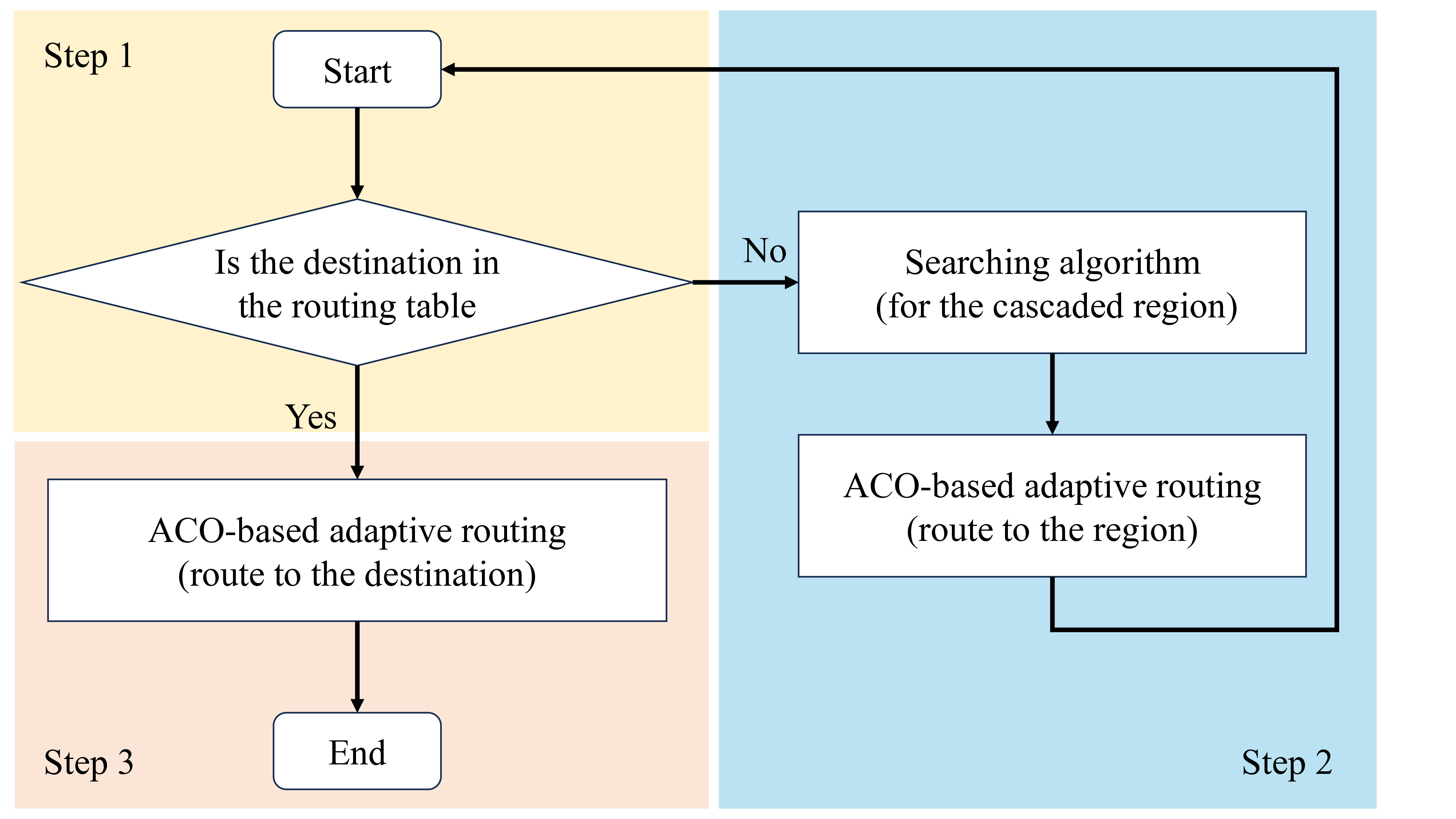

3.2. Evaluation 4. Regional ACO-Based Cascaded Adaptive Routing in Mesh-Based Network-on-Chip System 4.1. ACO Introduction and Customization of Routing Algorithm 4.2. Proposed Technique for Regional ACO 4.3. RACO-Based Cascaded Adaptive Routing 4.4. Implementation and Evaluation 5. A High Performance Selection Strategy with Low Power Consumption: DBSS 5.1. Existing Problems 5.2. DBSS 5.3. Routing Functions 5.4. Evaluation 5.4.1. Evaluation of Different Routing Functions 5.4.2. Evaluation on Different Selection Strategies 5.5. Hardware Overhead 5.5.1. Wiring Overhead Table 1: Wiring Overhead of Different Selection Strategies 5.5.2. Power Consumption 6. Conclusion Acknowledgment

To evaluate the real communication traffic circumstance, a MultiMedia System (mms) is involved. Packet injection rate(pir) ranging from zero to one is the rate at which packets are injected. The pir is in the model of packets/cycle/node, and a pir represents that 0.1 packets are sent by every node in every clock cycle or a packet is sent by every node in every 10 clock cycles. Throughput and delay are used as performance metrics. Throughput is defined as follows:

\[ TP=\frac{\textit { Total received flits }}{\textit { Number of nodes } \times \textit { Total cycles }} {, } \]

where Total received flits is the sum of how many flits reach the targeted nodes, The total cycle is the sum of clock cycles that pass from the generation of the first message to the receive of the final message, and Total cycles is the number of clock cycles. Delay is the sum of clock cycles between the injection and the reception at the target node. Average delay, D, is shown as follows:

\[ D=\frac{1}{K} \sum_{i=1}^{K} D_{i} {, } \]

where K is the sum of messages getting to their target nodes and \(D_{i}\) is the delay of message i [4]. 8-flit packets are injected into a \(8 \times 8\) mesh NoC with random distribution. Every FIFO buffer has four flits. Before each beginning, the simulation is run for 10,000 cycles to keep stable and then executes for 20,000 cycles.

DBSS has a moderate wiring overhead much lower than RCA and NoP, and a little higher than LOCAL.

Selection Strategy

DBSS

RCA

NoP

LOCAL

Wire per Dimension

8

16

24

4

References

[1]. P. Guerrier and A. Greiner. A generic architecture for on-chip packet-switched interconnections. In Proceedings Design, Automation and Test in Europe Conference and Exhibition 2000 (Cat. No. PR00537), pages 250–256, 2000.

[2]. En-Jui Chang, Hsien-Kai Hsin, Chih-Hao Chao, Shu-Yen Lin, and An-Yeu Wu. Regional acobased cascaded adaptive routing for traffic balancing in mesh-based network-on-chip systems. IEEE Transactions on Computers, 64(3):868–875, 2015.

[3]. Sheng Ma, Natalie Enright Jerger, Zhiying Wang, Mingche Lai, and Libo Huang. Holistic routing algorithm design to support workload consolidation in nocs. IEEE Transactions on Computers, 63(3):529–542, 2012.

[4]. Giuseppe Ascia, Vincenzo Catania, Maurizio Palesi, and Davide Patti. Implementation and analysis of a new selection strategy for adaptive routing in networks-on-chip. IEEE transactions on computers, 57(6):809–820, 2008.

[5]. Maurizio Palesi, Rickard Holsmark, Shashi Kumar, and Vincenzo Catania. Application specific routing algorithms for networks on chip. IEEE Transactions on Parallel and Distributed Systems, 20(3):316–330, 2009.

Cite this article

Sun,Y.;Qian,X.;Qu,X. (2025). Adaptive Routing Algorithms of Network-on-Chip: A Literature Review. Applied and Computational Engineering,132,212-224.

Data availability

The datasets used and/or analyzed during the current study will be available from the authors upon reasonable request.

Disclaimer/Publisher's Note

The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of EWA Publishing and/or the editor(s). EWA Publishing and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content.

About volume

Volume title: Proceedings of the 2nd International Conference on Machine Learning and Automation

© 2024 by the author(s). Licensee EWA Publishing, Oxford, UK. This article is an open access article distributed under the terms and

conditions of the Creative Commons Attribution (CC BY) license. Authors who

publish this series agree to the following terms:

1. Authors retain copyright and grant the series right of first publication with the work simultaneously licensed under a Creative Commons

Attribution License that allows others to share the work with an acknowledgment of the work's authorship and initial publication in this

series.

2. Authors are able to enter into separate, additional contractual arrangements for the non-exclusive distribution of the series's published

version of the work (e.g., post it to an institutional repository or publish it in a book), with an acknowledgment of its initial

publication in this series.

3. Authors are permitted and encouraged to post their work online (e.g., in institutional repositories or on their website) prior to and

during the submission process, as it can lead to productive exchanges, as well as earlier and greater citation of published work (See

Open access policy for details).

References

[1]. P. Guerrier and A. Greiner. A generic architecture for on-chip packet-switched interconnections. In Proceedings Design, Automation and Test in Europe Conference and Exhibition 2000 (Cat. No. PR00537), pages 250–256, 2000.

[2]. En-Jui Chang, Hsien-Kai Hsin, Chih-Hao Chao, Shu-Yen Lin, and An-Yeu Wu. Regional acobased cascaded adaptive routing for traffic balancing in mesh-based network-on-chip systems. IEEE Transactions on Computers, 64(3):868–875, 2015.

[3]. Sheng Ma, Natalie Enright Jerger, Zhiying Wang, Mingche Lai, and Libo Huang. Holistic routing algorithm design to support workload consolidation in nocs. IEEE Transactions on Computers, 63(3):529–542, 2012.

[4]. Giuseppe Ascia, Vincenzo Catania, Maurizio Palesi, and Davide Patti. Implementation and analysis of a new selection strategy for adaptive routing in networks-on-chip. IEEE transactions on computers, 57(6):809–820, 2008.

[5]. Maurizio Palesi, Rickard Holsmark, Shashi Kumar, and Vincenzo Catania. Application specific routing algorithms for networks on chip. IEEE Transactions on Parallel and Distributed Systems, 20(3):316–330, 2009.